PCIe uses the popular point-to-point serial connection in the industry, which improves the data transmission frequency while ensuring compatibility. The first version of PCIe was released in 2003 and PCI Express 6.0 is also expected to be released in 2021. You can know detailed information about it through this post.

What Is PCIe?

Intel officially renamed 3GIO to Peripheral Component Interconnect Express on July 23, 2002. As an important branch of the computer bus, Intel adopted the popular point-to-point serial connection in the industry, which improved the standard of serial communication systems. Its interface varies depending on the bus width.

Most personal computers’ graphics cards, SSDs, Ethernet hardware, Wi-Fi, hard drives connections use PCIe as motherboard connection.

Different Versions of PCIe

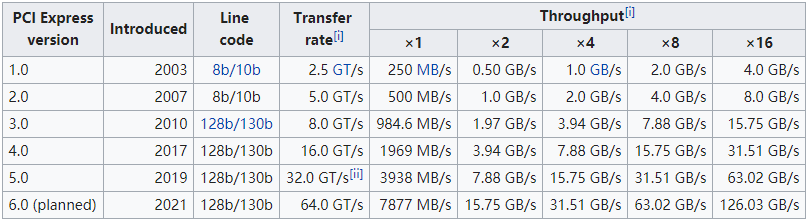

Since the release of PCI Express 1.0a in 2003, after many adjustments and improvements, several versions of PCI Express have been released, and PCI Express 6.0 may be released in 2021.

PCI Express 1.0a and 1.1

PCI-SIG released PCIe 1.0a in 2003, the data rate per lane reached 250 MB/s, and the transmission rate reached 2.5GT/s. The PCIe 1.1 introduced in 2005 only made some improvements without improving the data rate.

PCI Express 2.0 and 2.1

The PCI Express 2.0 introduced by PCI-SIG in 2007 increasing the data rate per lane to 500MB/s, so the 32-lane PCIe connector can support up to 16 GB/s transfer speed.

In addition, PCIe 2.0 motherboard slots are fully backward compatible, while PCIe 2.0 cards are basically backward compatible. PCIe 2.0 has improved the point-to-point data transfer protocol. It can provide data rates per lane up to 4 Gbit/s from its raw data rate of 5 GT/s.

PCIe 2.1 supports most of the management, support, and troubleshooting systems to be implemented in PCI Express 3.0, but PCIe 2.1 cards are not compatible with some older motherboards with 1.0/1.1a d due to the increase in power from the slot.

PCI Express 3.0 and 3.1

In November 2010, PCI-SIG introduced PCI Express 3.0 with 8 GT/s transfer rate. The PCIe 3.0 encoding scheme changed from the previous 8b/10b to the more efficient 128b/130b, reducing the 20% bandwidth overhead of PCIe 2.0 to 1.54%, and other specifications are basically unchanged. In addition, PCIe 3.0 also supports backward compatibility.

In addition to a significant increase in bandwidth data throughput, PCIe 3.0 has a faster signal speed and a lower data transmission delay. PCIe 3.0 also optimizes enhanced signaling and data integrity.

PCIe 3.1, which released in November 2014, improved power management, performance and functionality compared to PCIe 3.0.

PCI Express 4.0

Released on June 8, 2017, PCIe 4.0 delivers 16 GT/s bit rate, twice the bandwidth offered by PCIe 3.0, and provides backwards and forwards compatibility, improves flexibility, scalability and low power consumption.

PCI Express 5.0

PCI Express 5.0 was officially released on May 29, 2019, and the bandwidth has increased to 32 GT/s. In a 16-channel configuration, 63GB/s is produced in each direction.

PCI Express 6.0

PCIe 6.0 is expected to be released in 2021, and its bandwidth will increase to 64 GT/s, with 128 GB/s in each direction in a 16-channel configuration.

Advantages of PCIe

The PCIe bus uses a point-to-point serial connection device connection, which means that each PCIe device has its own independent data connection, and the concurrent data transmission between each device does not affect each other.

The PCIe bus uses the serial connection feature to bring the data transfer speed to a very high frequency, and its transfer rate varies according to the bit width of the bus. In addition, the PCIe bus supports bidirectional transmission mode, providing higher transmission rates and quality.

Hardware Protocol of PCIe

PCIe is a layered protocol combined with a transaction layer, a data link layer, and a physical layer.

Transaction Layer

PCIe allows the link to carry other traffic when the target device collects response data by adopting a split transaction method. It uses trusted flow control.

Data Link Layer

The data link layer sorts the transaction layer packets generated by the transaction layer, and can reliably pass TLP between the two endpoints: Ack that can pass LCRC checksum continuity check is called Ack (command correct response); TLPs that pass the check are called Nak (no answer), TLPs that do not respond, or TLPs that wait for a timeout are retransmitted.

Physical Layer

The physical layer can be divided into electrical and logical specifications, and the logical specification can be divided into MAC and PCS. At the electrical level, each channel consists of two unidirectional differential pairs, with separate differential pairs for transmission and reception, and a total of four data lines per lane.

The connection between the two PCIe devices is the link. Because the device can choose to support 2, 4, 8, 12, 16, 32 channel links, there are two ways to achieve good compatibility.

Apply of PCIe

PCIe is used in consumer, server and industrial applications. In 2005, almost all personal computer motherboards used PCIe. As of 2013, PCIe has successfully replaced AGP as the default interface for graphics cards on new systems. PCIe is now used in all types of network cards, sound cards, graphics cards, and current NVMe SSDs.